新闻资讯

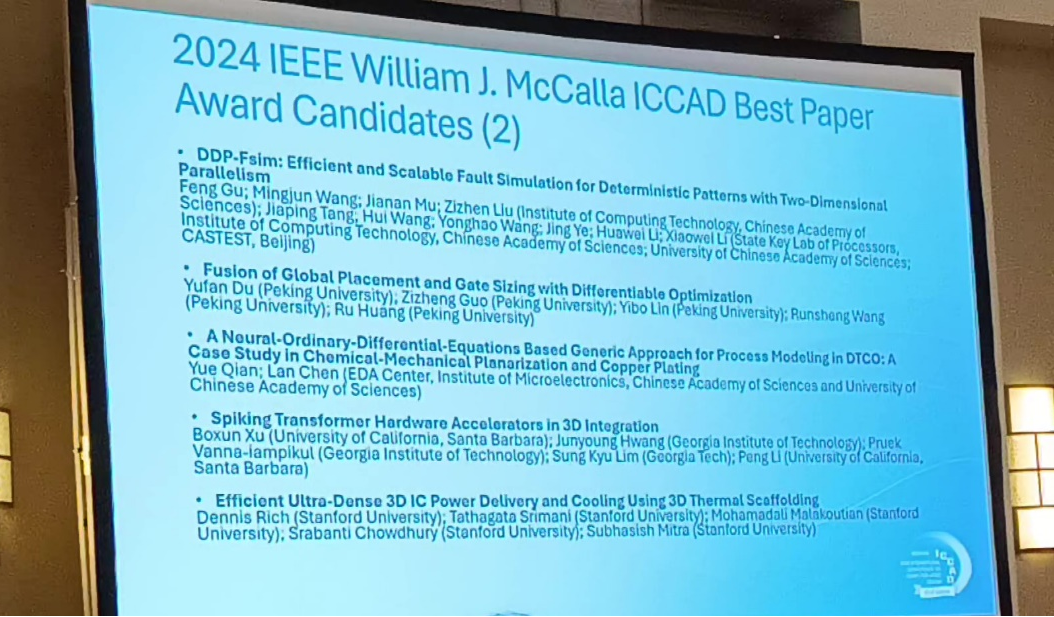

实验室研究成果获得ICCAD 2024最佳论文提名

时间:2024-12-30

随着半导体工艺节点的微缩和集成电路设计复杂度的提升,可测试性设计(DFT)成为超大规模数字集成电路设计的一个重要环节,以确保自动测试向量生成(ATPG)的故障覆盖率。在DFT过程中,故障仿真用于评估和验证设计在制造过程中可能出现的缺陷是否能被有效检测,其性能直接影响ATPG算法效率。近年来,多核处理器架构的普及推动了并行故障仿真方法的发展,通过将任务分配到多个核心上执行,大幅提升了仿真效率。然而,现有方法多侧重于优化随机向量的仿真速度,忽视了对ATPG生成的确定型向量的仿真优化。该文提出的DDP-Fsim算法,基于确定型向量的特点划分了故障维度并行和向量维度并行两个阶段,并引入无扇出区域作为理想的调度单位,优化了负载均衡和调度开销,避免了重复计算。实验结果表明,DDP-Fsim在24核系统上相较于单核系统加速比达到16倍,而主流商业工具仅能达到3至6倍的加速比。在处理大型电路时,DDP-Fsim依然保持了稳定的加速比,验证了其在工业应用中的优越性。论文中提出的技术,曾用于EDA2难题挑战赛(侠客岛)的打榜赛题“基于ARM多核CPU架构的故障仿真并行加速” (海思出题)。2024年3月,处理器芯片全国重点实验室的研究生谷丰、王铭珺和汤家平(论文作者)组队完成的竞赛成果从数十支竞赛队伍中脱颖而出,获得该项赛题的第一名。

由电气电子工程师学会(IEEE)和美国计算机学会(ACM)共同主办的国际计算机辅助设计会议(ICCAD)在电子设计自动化领域享有很高的国际学术地位和广泛的影响力。第43届ICCAD于2024年10月27日至10月31日在美国新泽西州纽瓦克举行,共录用论文195篇,其中10篇论文获得最佳论文提名,最终2篇论文获得最佳论文。