研究成果

处理器芯片全国重点实验室多项研究成果获MICRO 2025录用

在2025年的体系结构领域顶级会议MICRO (IEEE/ACM International Symposium on Microarchitecture ,CCF-A类)上,中国科学院计算技术研究所处理器芯片全国重点实验室(以下简称“实验室”)多项研究成果获录用。

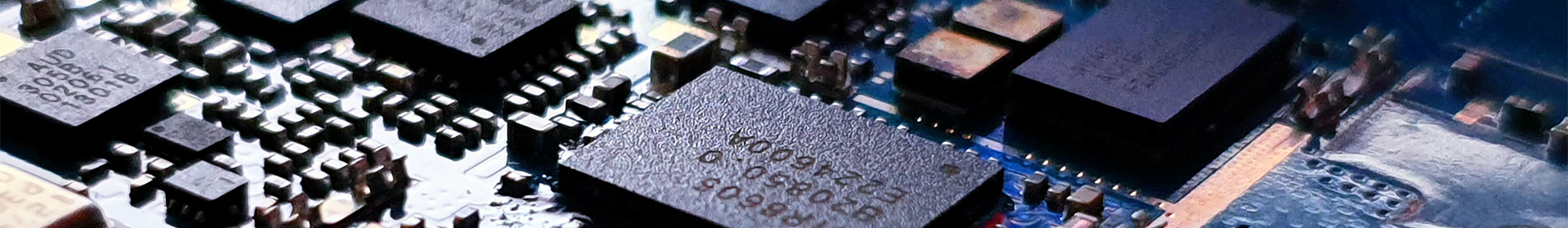

《Athena: Accelerating Quantized Convolutional Neural Networks under Fully Homomorphic Encryption》

第一作者为实验室集成电路课题组博士生杨英豪,指导教师为路航副研究员和李晓维研究员。Athena是面向量化卷积神经网络(QCNN)密态推理的软硬件协同设计FHE加速系统,包括算法推理框架和硬件加速架构。在传统基于CKKS同态加密方案的CNN推理中,由于对高数据精度以及多样非线性函数的需求,往往会面临加密参数大、函数拟合精度难以控制以及硬件不友好的问题,难以实现通用且高效的密态推理解决方案。本文提出的Athena将视角大胆转向量化技术,巧妙利用量化精度需求低的特点,结合丰富的密码学技术软硬件协同地设计了高效、硬件友好且易用的量化CNN推理框架和加速器架构,能够灵活支持不同的量化精度,相较于传统FHE加速方案在性能和芯片面积上都获得了大幅提升,说明了量化在FHE加速上的潜力,有望未来进一步扩展和适配到密态大语言模型(LLM)的推理中。

图: Athena算法推理框架和硬件加速架构

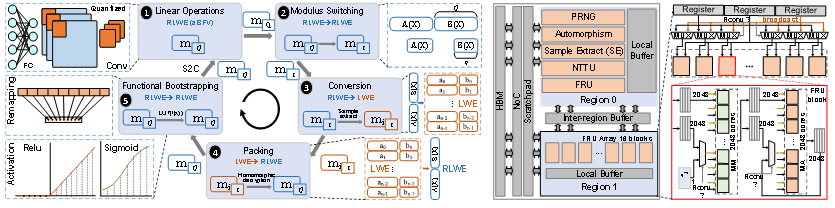

《DiffTest-H: Toward Semantic-Aware Communication in Hardware-Accelerated Processor Verification》

第一作者为实验室硕士生游昆霖,指导老师为包云岗研究员。DiffTest-H是基于FPGA等硬件仿真平台加速的处理器核协同仿真验证框架,针对“香山”开源高性能RISC-V处理器,达到9.8MHz的协同仿真速度,同时保留逐指令粒度的出错后调试能力。DiffTest-H已开源并集成进“香山”项目的MinJie开发工具链,实际应用于“香山”处理器的功能验证,在过去6个月内发现超过150个复杂 Bug。

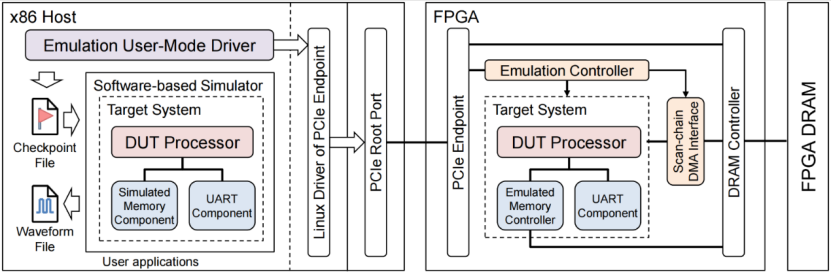

基于团队前期DiffTest协同仿真验证框架(MICRO’22),DiffTest-H将待测设计(DUT)和参考模型(REF)分别部署于FPGA等硬件仿真平台和软件侧上位机,通过软硬件通路传输验证信息。本工作利用验证数据语义,在优化软硬件通信需求的同时保留逐指令粒度的出错后调试能力:(1)Batch 通过数据打包降低通信频率,利用数据结构化信息打包不同结构、长度的验证数据,最小化传输空泡;(2)Squash 通过数据压缩减少数据量,基于语义依赖调度不同验证数据压缩,最大化压缩效率;(3)Replay 保留逐指令粒度的出错调试能力,支持出错压缩数据的回滚并进行逐指令重新传输、处理,精准定位错误。实验结果表明,DiffTest-H将通信频率降低43倍、数据量降低47倍、整体协同仿真加速98倍。

图:DiffTest-H 在双核“香山”处理器上的验证框架

Tutorial

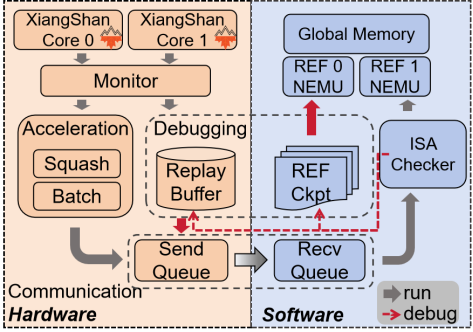

《XiangShan: An Open-Source High-Performance RISC-V Processor and Infrastructure for Architecture Research》

由全重团队主导研发的“香山”开源高性能处理器项目再次成功入选MICRO 2025 Tutorial。这是“香山”团队第九次入选体系结构四大顶会(MICRO/ISCA/HPCA/ASPLOS)的 Tutorial,彰显“香山”在开源处理器领域的持续引领地位。“香山”是一款全流程开源、具有工业级高性能与高可靠性的 RISC-V 处理器,其快速的设计迭代得益于团队自研的敏捷开发平台“MinJie”(Micro’22、IEEE MICRO Top Picks)。相较以往,本次 Tutorial 将重点介绍与“香山”处理器高度校准的软件模拟器 XS-GEM5,旨在降低研究者的架构探索门槛。活动将带领参会者亲自编译、仿真“香山”,并采用“MinJie”开发工具链及 XS-GEM5 模拟器,实现快速上手的架构探索与错误调试。一直以来,“香山”团队不仅在学术前沿不断突破,也持续在 RISC-V 中国、欧洲峰会等重要国际会议中开展 Tutorial 活动,积极推广开源芯片理念,分享“香山”处理器的敏捷开发经验。

图:“香山”开源处理器“MinJie”开发工具链

Tutorial

《REMU: An FPGA-based Open-source Replayable EMulator for System-level Evaluating and Debugging Processors》

全重团队的开源FPGA加速仿真工具框架(REMU)入选MICRO 2025 Tutorial。REMU通过FPGA硬件检查点与确定性回放技术实现待测处理器核及系统级部件(如内存与存储)的比特精确与周期精确的完整可见性,并支持集成真实PCIe外部设备以完成系统级原型评测。本次Tutorial将在ISCA 2024 Tutorial的基础上扩展新的内存和存储模型,并带领参会者通过真实的实践案例(香山开源RISC-V处理器核与外设)从系统级视角学习并体验REMU工具,从而实现软硬件系统级协同调试。

MICRO

MICRO 主要收录计算机体系结构领域在微体系结构设计、处理器架构、软硬件协同优化、高性能计算以及新兴计算范式等方向的最新研究成果。自 1968 年创办以来,MICRO 已成为该领域历史最为悠久且最具学术影响力的顶级国际会议之一,对推动微体系结构及相关领域的发展起到了重要作用。第 58 届 MICRO 会议将会在韩国首尔举行,本届会议的录用率为 20.8%(包括conditional accept)。