研究成果

实验室成果入选ICCAD2025并获后端最佳提名

国际计算机辅助设计大会(International Conference on Computer-Aided Design,ICCAD),是电子设计自动化(EDA)和计算机辅助设计领域的顶级会议之一,2025年该会议在德国慕尼黑举办。实验室论文《CLASS: A Controller-Centric Layout Synthesizer for Dynamic Quantum Circuits》被ICCAD 2025接收,并获得后端最佳论文提名。该论文共同第一作者为实验室智能计算机课题组博士生陈禹和赵逸伦,指导教师为王颖研究员和韩银和研究员。

从“量子芯片”到“控制器”:重新定义布局综合问题

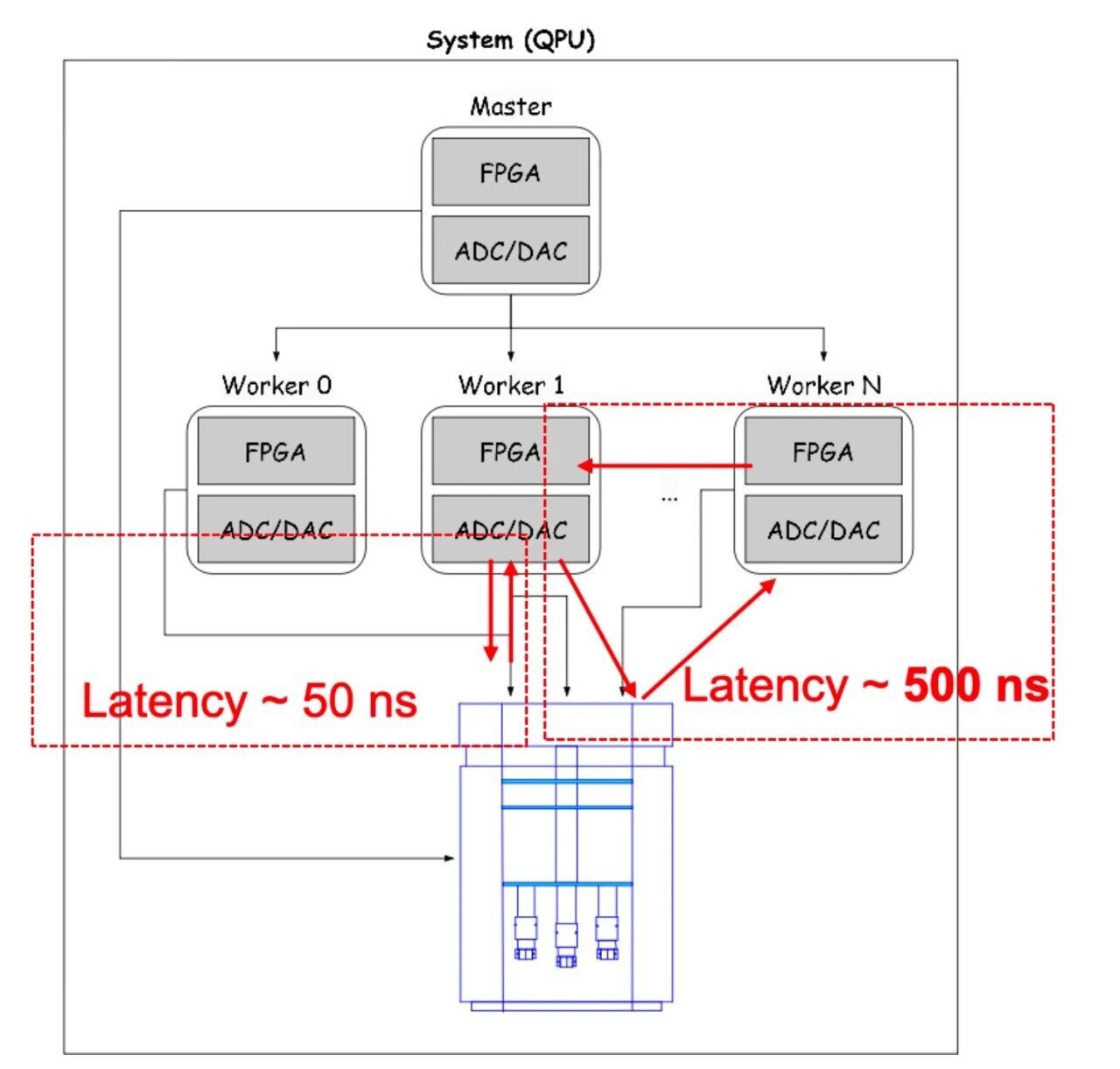

在经典计算机中,EDA工具通过自动化设计实现从逻辑综合到布局布线的全流程优化。而在量子计算机中,“布局综合(Layout Synthesis)”承担着类似角色,是量子算法映射到物理硬件的关键步骤。然而,随着量子比特数从几十迈向上千甚至上百万规模,量子系统的控制架构也从单控制器演化为多控制器协同架构。这类分布式控制架构由多个量子控制处理器(Quantum Control Processor, QCP)互联组成——它们共同驱动量子芯片执行复杂的量子操作。

在这种架构下,控制器间通信延迟成为系统性能的最大瓶颈。尤其是在执行动态量子电路(Dynamic Quantum Circuits)时,这一问题尤为突出。动态电路允许在计算过程中根据测量结果“前馈”调整后续操作,这是量子纠错、量子隐形传态等核心算法的基础。但如果测量结果需要跨控制器传输,就会引入严重延迟,造成量子态退相干(Decoherence)——即计算失效。

CLASS:以控制器为中心的量子布局综合新模式

为应对这一挑战,研究团队提出了CLASS(Controller-centric Layout Synthesizer System)——首个面向动态量子电路的控制器感知布局综合框架。与传统“以量子芯片为中心”的方法不同,CLASS将优化重心转向“以控制器为中心”,并创新性地将布局问题建模为超图最小割(Hypergraph Min-Cut)问题。

其核心算法分为两阶段:

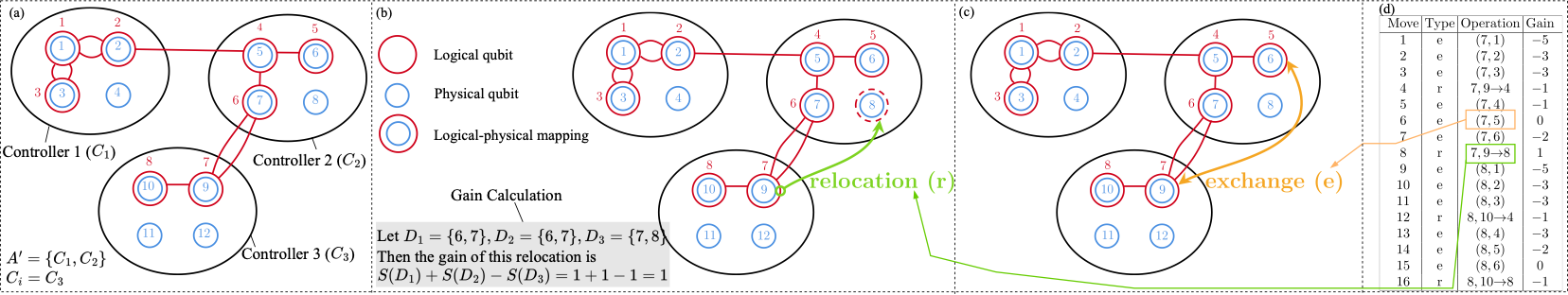

1. 初始布局生成:基于贪心策略,将强依赖的量子比特优先分配至同一控制器。

2. 迭代优化阶段:通过量子比特迁移与门级调度协同优化,进一步减少跨控制器通信。

对于存在拓扑约束的量子芯片,CLASS还引入了延迟感知门调度器(Latency-Aware Scheduler),在插入SWAP门时同时权衡电路深度与通信时延。

在多项标准测试电路中,CLASS实现了平均48.45%的跨控制器通信减少,部分电路的通信成本降至零,同时量子操作数仅增加约2.10%。这意味着CLASS在保持电路正确性的同时显著提升执行效率,适用于当前超导、离子阱等主流技术路线在扩展到百比特以上规模时面临的控制瓶颈问题,为未来大规模量子计算的可扩展性提供技术基础。

该研究兼具应用价值,CLASS可作为量子EDA中的节点工具,直接集成至国产量子计算云平台(如OriginQ、Quafu等)的编译器工具链中,为量子系统在芯片-控制协同设计和软硬件适配方面提供新思路。

图1 QPU(量子处理器)控制架构中的测量-前馈路径及其时延

图2 CLASS基于量子比特移动的迭代优化减少跨控制器通信