处理器芯片全国重点实验室为提高实验室的开放层次,提高学术水平和技术水平,增进国内外学术交流与合作,促进人才流动与学科交叉渗透,按照相关规定特设开放研究课题。欢迎国内外相关领域的科研工作者参与实验室的开放课题研究。

1、根据我国处理器芯片领域的发展战略,着眼于国民经济建设的当前和长远的需要和国际学科发展的前沿;

2、鼓励具有开拓性、前瞻性、创造性和高层次理论和技术的自主创新研究及具有重大应用前景的项目;

3、利于促进多学科的交叉渗透和多部门的联合攻关,有利于建立和发展国际合作的新格局,有利于人才培养和学科的发展;

4、鼓励和支持具备博士学位、高级职称的国内外科技工作者申请;

5、资助项目的申请者要求与本实验室科研人员协同工作。

6、项目资助5万/项,资助周期一般不超过2年。

本年度建议开展课题如下(可不限于以下课题):

处理器新型供电网络下的快速功耗管理--集成式电压调节器支持的处理器微秒级电压频率调节

研究内容: 芯片集成电压调节器正逐渐成为高端处理器,尤其是异构集成Chiplet封装下的处理器新型供电方式。其最大优点就是可以在纳秒的响应时间内调节处理供电电压,从而实现微秒级的处理器电压动态调节。经过相关原型测试,微秒级的处理器电压动态调节可显著降低处理器功耗。然而尚缺乏有效的微秒级的处理器电压动态调节的理论分析及具体设计优化方法。该部分内容旨在研究基于模型和数据的处理器运行状态细粒度在线预测方法。利用预测结果对电压频率调节进行指导,实现微秒级电压频率调节,降低处理器功耗。本部分研究将利用处理器性能寄存器中的参数,以多核及众核处理器架构,建立普适并具有较高精度的处理器状态细粒度预测。采用定义并求取粗粒度(毫秒级)架构层计算性能/功耗指数,与细粒度(微秒级)电路层性能功耗实时采样测量的方法,对处理器微秒级运行状态进行统一量化描述。结合处理器细粒度状态预测,设计结合用户指令、架构层、电路层信息的层次化的微秒级功耗管理机制,最终实现处理器微秒级功耗管理。

题目2

基于MRAM的存内计算电路与器件的协同设计方法

研究内容: 存内计算是克服冯诺依曼处理架构性能墙和功耗墙的有效技术途径之一。基于电子自旋的磁随机存储器具有非易失性、超长耐久度、超快读写、低功耗等优点,是未来实现新型存储和计算的潜在技术之一。然而,MRAM存储器件具有显著的小电阻特性,使用经典的交叉阵列结构实现存内计算时,会产生较大的电流,导致存内计算功耗的显著增加。为此,本项目拟研究基于MRAM的新原理器件与电路协同设计方法,设计一套MRAM存内计算电路-器件的协同优化工具,实现MRAM存内计算芯片的超低功耗优化。具体内容主要包括三个方面:1、研究自旋轨道矩(SOT)与自旋转移矩协同器件、SOT与电压调控磁各向异性协同器件等新型MRAM单元,通过电学驱动磁性层无场翻转,实现超低功耗的自旋轨道矩翻转以及存储介质的优化。2、研究基于多数门逻辑的算术逻辑电路与MRAM器件的结合方法,探索适用于SOT-MRAM的新型存内计算电路结构,替代经典的交叉阵列的存内计算模式,降低MRAM存内计算电路功耗。3、研究MRAM存内计算电路与MRAM器件的跨层优化方法,解决分层设计导致的局部优化问题,利用机器学习技术,实现高效的电路-器件跨层优化设计空间探索,开发一套面向MRAM存内计算芯片的电路-器件自动化超低功耗优化工具。

研究内容: 研究通用用户态存储面临的通用性和轻量化问题,为用户态存储提供足够的功能支撑,满足传统应用程序的功能需求,便于传统应用程序往用户态存储方向移植;研究用户态的页缓存及其管理组件,实现页缓存从传统存储软件栈中解耦,下放到计算型固态存储中并借助于SSD固件实现控制和管理;研究用户态页缺失处理机制,实现用户态的demand paging;基于定制的用户态demand paging、用户态存储设备驱动和SSD管理的页缓存系统,研究用户态mmap;研究多计算型存储器的资源聚合,实现对页缓存管理、demand paging和mmap的并行访问和处理。

基于近存储计算FPGA系统级原型平台的任务划分及调度技术研究

研究内容: 随着应用数据处理规模激增,处理器与存储介质之间的数据移动开销逐渐成为瓶颈。无论是传统的联机分析处理(OLAP)应用,还是近年来兴起的神经网络和图计算等,都呈现出较缓存命中率低的严峻问题。在这些数据密集型应用的处理过程中,处理器到存储器间的数据传输量大,导致系统的性能下降且能耗变高。针对传统体系结构的局限性,利用近存储计算技术将计算卸载到存储侧以减少数据的搬移,为高性能和高能率处理数据密集型的任务带来了机遇与挑战。另一方面,未来近存储计算芯片有望将计算单元与存储器件进行高密度集成,但同时也增加了芯片的设计难度。为了保证近存储计算芯片设计的成功率,亟需在设计早期就为近存储计算芯片设计提供较为完整的硅前系统级功能验证平台,并配合计算任务划分及调度的自动化工具及性能评估方法。1、研究基于新型可计算存储硬件的任务划分和卸载,研究近存储算子设计技术,面向数据密集型任务需求提供比较选择、压缩解压、索引操作等数据处理加速功能,并根据新硬件特点进行算子执行优化设计。2、研究近存计算单元地址访问和地址信息维护策略,减小页表层级降低地址转换开销,实现在没有主机交互的情况下,在近存储端解释数据格式和原位访问数据。3、研究计算单元剩余计算资源评估、标识、记录和调度方法,基于硬件单元的计算特征和计算任务的数据特征,设计基于近存储架构的算子下推任务统一调度策略。4、结合实验室已有工作基础,探索近存储计算芯片FPGA硅前系统级评估平台的构建方法,支撑上述研究内容的系统级评测;同时通过将若干关键技术形成自动化工具,进一步构建较为完整的近存储计算芯片系统级集成开发环境。

基于硬件特性的跨平台二进制内核崩溃分析

研究内容: 针对现有内核程序缺乏二进制崩溃诊断技术以及软件监控技术会造成较大性能损耗的问题,针对不同平台的硬件追踪特性,设计构建跨平台的、统一的软硬件交互模式,并基于硬件追踪特性开展跨平台的内核崩溃分析技术研究,实现对二进制内核的崩溃成因诊断,为内核程序的漏洞修复提供支撑。考核指标:至少支持x86和ARM两种架构;漏洞定位的精确度达到90%以上;运行时的性能损耗在10%以下。

量子次模优化

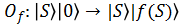

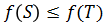

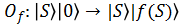

研究内容:本项目研究并设计次模优化问题的量子算法。在量子计算中,问题的输入可以用量子神谕模型表示。在这个模型中,每个集合S都被编码为量子态 。关于函数的量子神谕可以用复数域上的酉矩阵

。关于函数的量子神谕可以用复数域上的酉矩阵 表示。量子算法通过查询神谕

表示。量子算法通过查询神谕 获得关于的信息并求解相应的优化问题。由于

获得关于的信息并求解相应的优化问题。由于 是基底

是基底 上的复线性变换,因此对

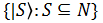

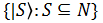

上的复线性变换,因此对 的一次查询包含了所有f(S)的信息。通过巧妙地操作这些信息,可能取得比经典算法性能更加优越的量子算法。关于量子神谕模型下次模优化问题的研究目前还是一片空白。因此,本项目只考虑如下两种简单的约束:1、无约束,即

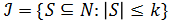

的一次查询包含了所有f(S)的信息。通过巧妙地操作这些信息,可能取得比经典算法性能更加优越的量子算法。关于量子神谕模型下次模优化问题的研究目前还是一片空白。因此,本项目只考虑如下两种简单的约束:1、无约束,即 ;2、基数约束,即

;2、基数约束,即 。在研究基数约束时,本项目假定次模函数是单调的,即对于任意集合

。在研究基数约束时,本项目假定次模函数是单调的,即对于任意集合 ,有

,有 。根据经典算法的研究进展,本项目拟从如下三个方面展开研究:1、在经典神谕模型下,对于无约束的情况,任何多项式算法的近似比不能超过1/2;对于基数约束,任何多项式算法的近似比不能超过 1-1/e。本项目希望探究在量子神谕模型下,多项式量子算法能否突破上述近似比的限制。2、在经典神谕模型下,对于无约束的情况,现有的1/2-近似算法需要线性时间,并且任何常数近似算法都需要几乎线性的时间。本项目希望探究在量子神谕模型下,是否存在平凡加速的量子算法,抑或任何量子算法都需要线性时间。3、在经典神谕模型下,对于基数约束,现有的(1-1/e)-算法需要线性时间。本项目希望探究在量子神谕模型下,是否存在更快的量子算法。

。根据经典算法的研究进展,本项目拟从如下三个方面展开研究:1、在经典神谕模型下,对于无约束的情况,任何多项式算法的近似比不能超过1/2;对于基数约束,任何多项式算法的近似比不能超过 1-1/e。本项目希望探究在量子神谕模型下,多项式量子算法能否突破上述近似比的限制。2、在经典神谕模型下,对于无约束的情况,现有的1/2-近似算法需要线性时间,并且任何常数近似算法都需要几乎线性的时间。本项目希望探究在量子神谕模型下,是否存在平凡加速的量子算法,抑或任何量子算法都需要线性时间。3、在经典神谕模型下,对于基数约束,现有的(1-1/e)-算法需要线性时间。本项目希望探究在量子神谕模型下,是否存在更快的量子算法。

面向高可靠边缘计算的容错神经网络协同设计优化

研究内容: 随着边缘计算和深度学习技术的迅猛发展, 深度神经网络越来越多地应用于高可靠嵌入式系统,如无人驾驶汽车、无人机、智能机器人等。但是深度神经网络不仅要面对外部黑客攻击的威胁,还要面对来自环境和自身的错误,因此深度神经网络容错设计优化成为当今高可信边缘计算领域的研究热点。不同于传统浅层神经网络,深度神经网络具有网络结构复杂、模型参数繁多、可解释性弱等特点,为容错深度神经网络设计优化带来了严峻的技术挑战。该项研究针对深度神经网络的不可容忍错误,剖析面向高可靠边缘计算场景的深度神经网络的常见错误类型,探索其容错方法,并提供面向高可靠边缘计算的量化神经网络的硬件加速器支持。研究内容主要包括:1、分析高可靠边缘计算中深度神经网络的常见错误类型,探索错误在深度神经网络中的传播条件,建立可解释的错误传播模型;2、针对高可靠边缘计算的资源受限问题,探索轻量级的量化深度神经网络出错阻断方法,设计高效率的深度神经网络容错方法;3、研究基于FPGA的容错神经网络协同设计优化方法,建立量化深度神经网络在FPGA上的出错隔离阻断和资源优化配置方案,为面向高可靠边缘计算的容错深度神经网络提供硬件加速。

面向人工智能大模型训练的DPU架构设计

研究内容: 本课题拟设计针对人工智能大模型训练的DPU架构,减少AI加速器的IO开销,提升AI加速器的计算利用率;将DPU集成入人工智能框架,从而提高AI加速器的利用率。具体内容如下:目前市面上已有不同的DPU,不过主要为云计算平台服务,并无为人工智能大模型训练服务,故设计并实现面向人工智能大模型训练的100Gbps DPU架构,支持AllReduce、AllGather、ReduceScatter等集合通信算子下沉到DPU,减少AI加速器的通讯量,从而缓解AI加速器IO瓶颈。目前DPU不能无法衔接主流人工智能框架,故需开发一套集合通信适配层,将DPU软件协议栈集成进主流人工智能框架,尽可能挖掘AI加速器计算与DPU软件协议栈提供的通信之间的并行,从而提高人工智能框架层面的并行度,从而提高AI加速器的利用率。同时,保持用户编程接口不变。

面向深度学习芯片的数据精度异常检测

研究内容:为更好地发挥芯片的处理能力,需要深入讨论以下问题:产业应用大量使用复合数据类型,这些数据是指由多个或多种基本数据类型组合而成的数据类型,通常需要精细化和专业化的解析方法,甚至需要配备专业的解码器。通过硬编码的方式为每种不同类型的文件匹配相应的解析代码和语义标注方法不仅工作量大,而且不断出现的新文件格式会使整个工作变得难以为继。因此,如何快速解析复杂多样的复合数据类型成为一个亟需解决的问题。通过建立应用服务调用链,可以利用技术手段对输入输出数据进行监控和分析,从而及时发现和解决数据类型不匹配引起的异常。由于第三方服务升级时间、频率等不可预知,为保障应用稳定性和可靠性,需要考虑实时性、稳定性和安全性等方面的要求,并对监控结果进行可视化和报警处理,以便及时发现和解决问题。具体步骤包括请求和响应数据的捕获、异常规则确定和匹配、异常行为分析等。在此过程中,将面临数据监控的高效性、异常规则的灵活性和兼容性、异常分析的准确性和实时性等需求和挑战。

面向数据搬运算子的张量管理单元体系结构研究与VLSI实现

研究内容:在当今科学计算、人工智能、图像渲染等算法中存在大量数据搬运算子,其对大规模张量进行各类变形操作,占用大量DRAM主存储器仿存带宽,却完全不需要或仅需搭配少量计算单元,该类算子并不适合部署于以高算力为特征的CPU、NPU或GPGPU上,其在当今人工智能算法中造成延时瓶颈。当前如NumPy程序库中已有50余项数据搬运算子(Array manipulation),本项目面向该类算子设计专用指令集、执行模型,聚焦传输粒度(Transfer-level)与字节粒度(Byte-level)数据搬运中的地址抽象、数据流重构关键技术,设计并实现张量管理单元(Tensor Manipulation Unit-TMU)并基于异构智能SoC进行功能、性能验证,目标对众多数据搬运算子实现高通用性、高通量、低物理开销的加速。2、面向传输粒度数据搬运算子的目标地址抽象机制研究3、面向字节粒度数据搬运算子的高效数据流重构机制研究4、张量管理器单元与CPU及NPU的协同处理机制研究

研究内容: 硬件层面加速同态加密成为研究热点,将同态加密算法中的计算开销大的部分通过专门的硬件设计,如专门的算子设计,针对性优化的数据访问模式或专用的多层次流水线设计可以大幅度提升全同态加密硬件的性能。该设计思想与AI加速器的设计融合,来达到整体的性能、功耗、面积的最优化目标,使得一套硬件加速器即具备全同态加密硬件加速能力,又具备一定AI加速的能力,需求二者的有机融合,是未来亟待解决的问题。重点研究内容包括:1、研究全同态加密硬件的加速器架构,包括专用的硬件加速算子单元、高效率的片上互联和存储访问特性,突破数据高并发等难题提升全同态加密的硬件性能。2、研究适用的AI加速器与全同态加密应用的场景,获取完整的待加速的算法结构,提取充分的领域加速算子,解决AI算子与同态加密算子融合的硬件架构3、开展全同态加密硬件与AI加速器融合硬件架构的仿真建模,并能够基本实现原型建模,进行系统级性能评估。

2023年度开放课题申请书电子版提交时间:2023年10月31日之前。 链接:https://pan.baidu.com/s/16fEC18LvJGVJEK3HmMFNjA?pwd=soqs

提取码:soqs

申请书电子版请传至:jinlin@ict.ac.cn

。关于函数的量子神谕可以用复数域上的酉矩阵

。关于函数的量子神谕可以用复数域上的酉矩阵 表示。量子算法通过查询神谕

表示。量子算法通过查询神谕 获得关于的信息并求解相应的优化问题。由于

获得关于的信息并求解相应的优化问题。由于 是基底

是基底 上的复线性变换,因此对

上的复线性变换,因此对 的一次查询包含了所有f(S)的信息。通过巧妙地操作这些信息,可能取得比经典算法性能更加优越的量子算法。

的一次查询包含了所有f(S)的信息。通过巧妙地操作这些信息,可能取得比经典算法性能更加优越的量子算法。 ;2、基数约束,即

;2、基数约束,即 。在研究基数约束时,本项目假定次模函数是单调的,即对于任意集合

。在研究基数约束时,本项目假定次模函数是单调的,即对于任意集合 ,有

,有 。根据经典算法的研究进展,本项目拟从如下三个方面展开研究:

。根据经典算法的研究进展,本项目拟从如下三个方面展开研究: